STM32MP1 SPI DMA Chip Select Delays #50730

Replies: 5 comments 14 replies

-

|

Do you have the Linux that runs in parallel on the Cortex-A? if no you can try to adapt one of the stm32cube SPI example in engineering mode to check if you have same issue. |

Beta Was this translation helpful? Give feedback.

-

|

Does it make any diff when GPIO is defined by |

Beta Was this translation helpful? Give feedback.

-

|

When the SPI transfer is using DMA, in the transceive_dma(), the spi_stm32_cs_control(dev, true) is setteing the CS pin a long time before the LL_SPI_EnableDMAReq_ which actually starts the transfer. This is just a WA since, the cs gpio should not be set (true) each loop but only at the beginning of the DMA transfer. |

Beta Was this translation helpful? Give feedback.

-

Beta Was this translation helpful? Give feedback.

-

|

Trying to setup and check the solution/WA in our case. |

Beta Was this translation helpful? Give feedback.

Uh oh!

There was an error while loading. Please reload this page.

Uh oh!

There was an error while loading. Please reload this page.

-

I am currently using Zephyr v3.0.0-rc3, and I have done work to add SPI DMA support for the STM32MP157 based on the work done in this PR #33913. I cross referenced those changes with the mainline and FRASTM/zephyr@dma_mp1, and I believe that they are correct. Also, SPI DMA has been verified to work with various SPI devices correctly.

The Issue

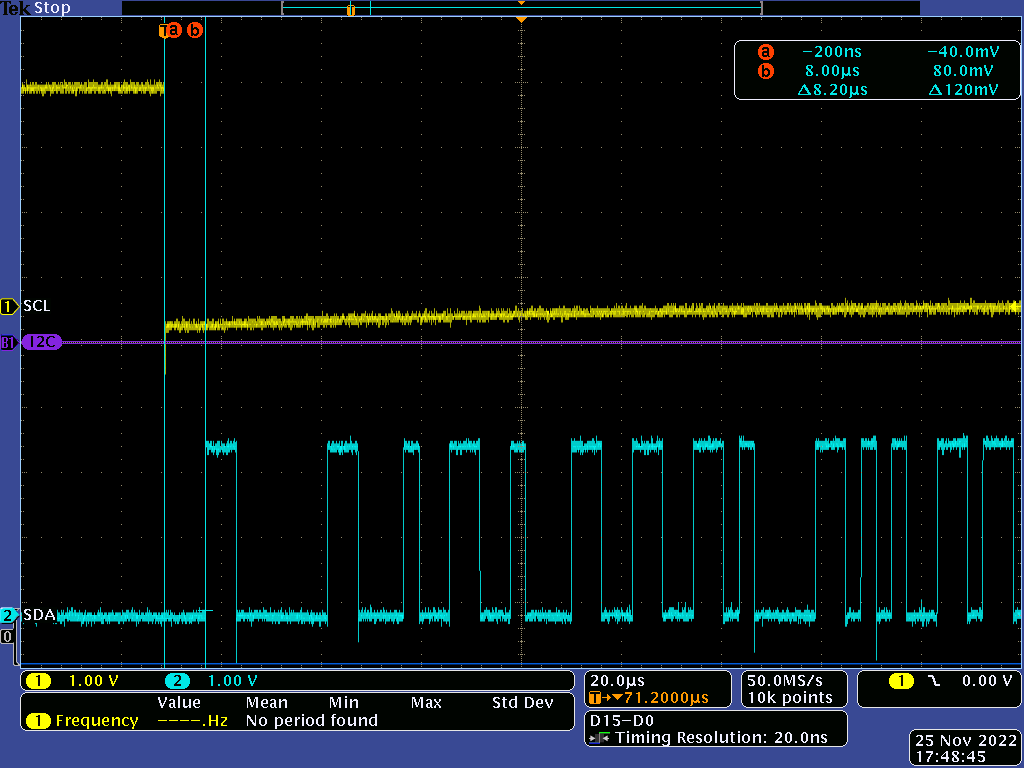

Prior to switching over to using SPI with DMA, I was using Async SPI with interrupts (i.e.,

CONFIG_SPI_ASYNC=y&CONFIG_SPI_STM32_INTERRUPT=y). I am talking to a SPI device (ATSENSE301, and I read 14 bytes (1 byte read command & 14 bytes response) from it every time I get an interrupt on the M4 from the ATSENSE301 that there's data to be read over SPI.Without DMA, the time from enabling/disabling the chip select (AFE_NSS) to the first/last clock edge was ~5us. See annotated logic capture below:

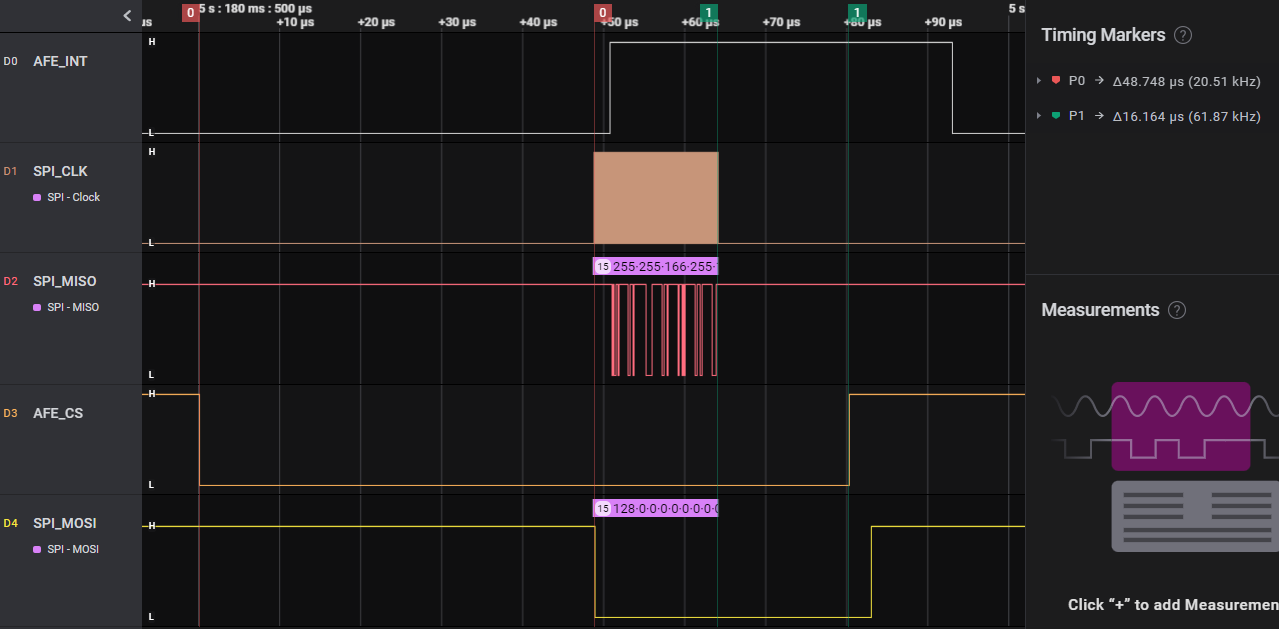

With DMA, there's a significant reduction in the amount of time it takes to clock data in/out which is great; however, the time from enabling/disabling the chip select (AFE_NSS) to the first/last clock edge has increased significantly (CS enable to first clock edge = ~49us, last clock edge to CS disable =~15us). See annotated logic capture below:

Based on the debugging that I have done (no profiling yet), these increased delays seem to be associated with calling into the DMA driver. I have traced the issue down to the

spi_dma_move_buffers()call intransceive_dma()in thespi_ll_stm32.cST SPI driver. Any thoughts or guidance on what can be optimized to minimize these delays would be extremely appreciated.CC: @erwango @arnopo @FRASTM @shlomow

Beta Was this translation helpful? Give feedback.

All reactions