i.mx RT600 changing flash base address #40091

-

|

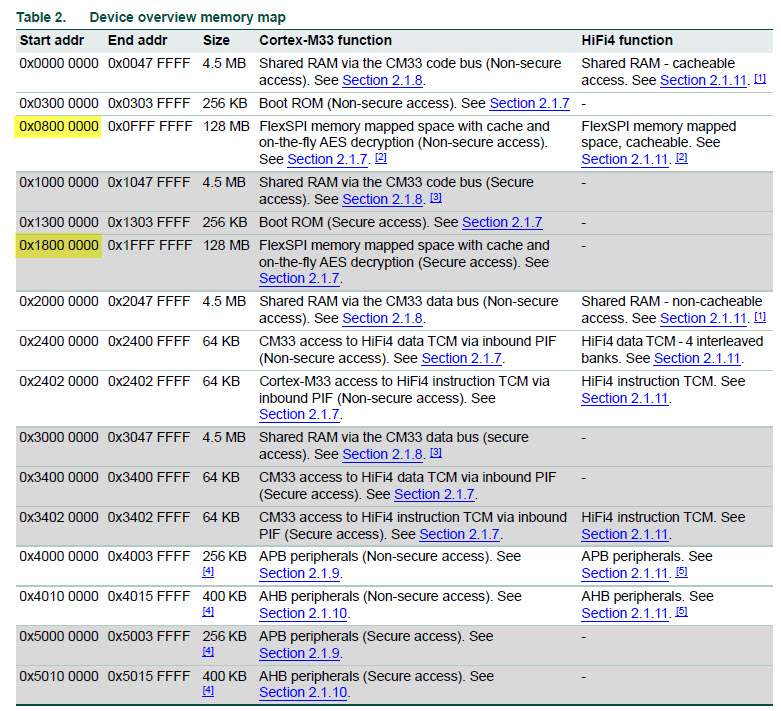

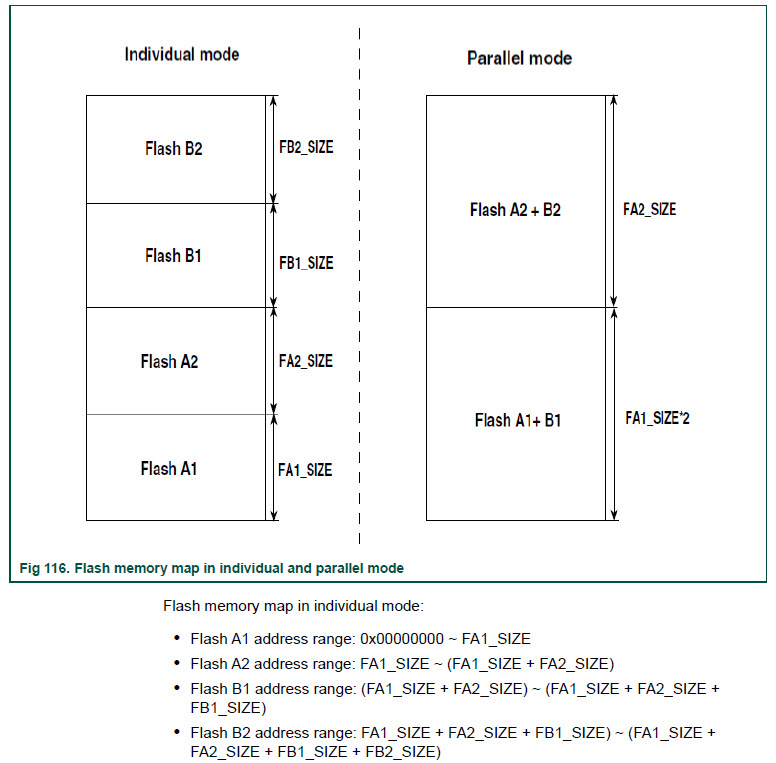

This is on behalf of Discord user emh203, who wrote this post, copied below: I am trying to find the maintainer for the RT6xx SoC port. I am working on a board port and ran into an issue with reworking the memory layout to use FlexSPI Port A. The Board for the RT685-EVK maps the base of Flash to 0x18000000. Using a QSPI device on FlexSPI a requires an address of 0x0800000. When I made the necessary changes in the device tree overlay in the board files, I noticed in the .map file that the base address of flash would always be 0x50000000. After some digging, I found the peripheral node in rt6xx.dtsi: }; I am able to patch my device tree with an overlay but It would be nice to get this upstream. I first would like to understand any possible implications of opening up the peripheral range. I could submit a pull request once this is sorted out. |

Beta Was this translation helpful? Give feedback.

Replies: 4 comments 3 replies

-

Beta Was this translation helpful? Give feedback.

-

|

Sounds good, @ehughes Yes I agree, I would put the QSPI boot header in your board folder. That is a good option for any memories not on the NXP EVKs, or any other differences with your boards. Best regards |

Beta Was this translation helpful? Give feedback.

-

|

@ehughes, I've been looking at this problem after @DerekSnell brought it to my attention. The baseline problem is with the definition of flexspi in the board level dts file because here it is defining/establishing both the register mapping addresses and the memory map addresses to the flexspi. Typically, for platforms that can support secure/non-secure builds, the definitions would be offsets from a base where the base gets set in the parent nodes defined in the soc dts files for secure vs non-secure (see nxp_rt6xx_ns.dtsi and nxp_rtxx.dtsi). But part of the problem here is that this base value is applied for both of the reg address definitions below which is problematic because as you are probably aware, the IO mapping and memory mapping are different base addresses and can't use a single base address. Still investigating. &flexspi { |

Beta Was this translation helpful? Give feedback.

-

|

@ehughes, check out the PR linked below. Basically, we needed to clean up the DTS definition for rt6xx and make a minor extension to the tools to ensure that this works as expected. The PR is only adding the SOC definitions for secure and non-secure builds. I did not add the board level targets as I'm not sure what the use case is for non-secure unless you have TFM. But this should give you the framework to understand how to get this to generally work if you are building for non-secure. |

Beta Was this translation helpful? Give feedback.

@ehughes, check out the PR linked below.

Basically, we needed to clean up the DTS definition for rt6xx and make a minor extension to the tools to ensure that this works as expected. The PR is only adding the SOC definitions for secure and non-secure builds. I did not add the board level targets as I'm not sure what the use case is for non-secure unless you have TFM. But this should give you the framework to understand how to get this to generally work if you are building for non-secure.

#40228